| |

|

Проектирование

схем применения с цифровыми гальваническими развязками |

|

В

статье приведено подробное описание семейства микросхем цифровых

гальванических развязок ISO72xx. Даны рекомендации по разработке топологии

печатных плат с этими микросхемами. Приведены расчетные соотношения и

графические зависимости, необходимые для разработки конструкции и

топологии печатных плат. В

статье приведено подробное описание семейства микросхем цифровых

гальванических развязок ISO72xx. Даны рекомендации по разработке топологии

печатных плат с этими микросхемами. Приведены расчетные соотношения и

графические зависимости, необходимые для разработки конструкции и

топологии печатных плат. |

Серия микросхем

ISO72xx на складе

|

|

Введение

Цель статьи –

помочь разработчикам в применении микросхем цифровых гальванических

развязок (ЦГР) семейства ISO77xx. В статье разъясняется принцип действия

гальванических развязок TI, указывается место размещения микросхем в

конструкции изделия, приводятся рекомендации по электромагнитной

совместимости при разработке топологии печатной платы.

Принцип действия

В микросхеме

ГР на рисунке 1 используется изолирующий конденсаторный барьер. Микросхема

состоит из двух каналов: высокочастотный канал предназначен для передачи

данных со скоростью от 100 кБ/с до 150 мБ/с, низкочастотный – для передачи

данных, начиная от сигналов постоянного тока до 100 кБ/с. Несимметричный

входной сигнал преобразуется в дифференциальный с помощью входного

инвертора.Далее резистивно-емкостная цепочка дифференцирует сигнал,

который затем преобразуется компараторами в дифференциальный импульсный

сигнал. С выхода компараторов сигнал поступает на триггер, состоящий из

элементов «ИЛИ-НЕ», далее с выхода мультивибратора сигнал поступает на

выходной мультиплексор. Логическая схема управления измеряет промежуток

времени между импульсами. Если промежуток между двумя последовательными

импульсами превышает установленный порог, то логическая схема

принудительно подключает выходной мультиплексор к

низкочастотному каналу. В нем используется емкость

большей величины, ШИМ-генератор для модуляции

сигнала несущей частотой встроенного генератора OSC.

Моду ляция необходима, чтобы увеличить частоту

сигнала и обеспечить его прохождение через конденсаторный

разделительный барьер. Из-за того что низкаячастота моду лируется высокой,

перед мультиплексором необходимо установить фильтр

низких частот (ФНЧ), для того чтобы отфильтровать

несущую частоту.

|

|

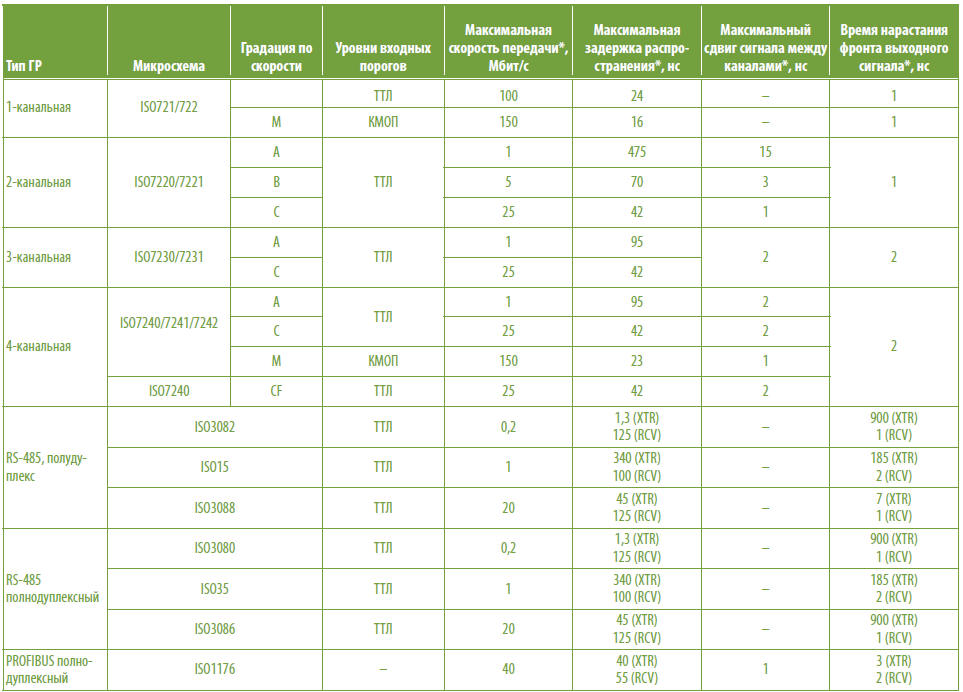

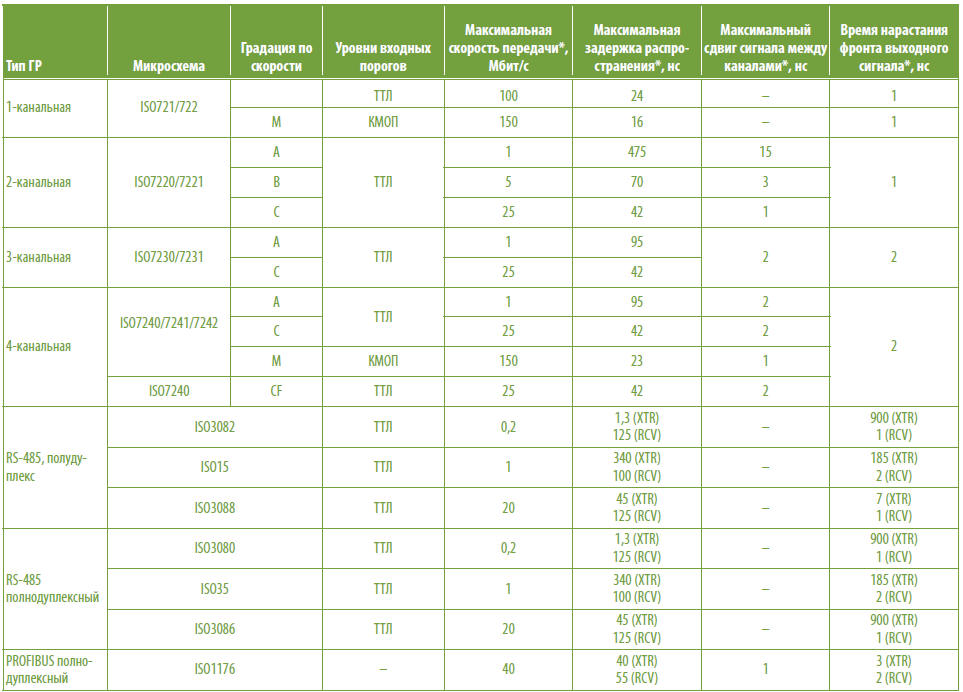

Таблица 1. Основные характеристики

микросхем ГР компании TI

Рис. 1. Структурная схема ЦГР

Рис. 2. Временные диаграммы

высокочастотного канала

Рис. 3. Временные диаграммы

низкочастотного канала

Рис. 4. Семейство микросхем ЦГР

|

|

Высокочастотный канал

На рисунке 2

показана схема высокочастотного канала и приведены временные диаграммы

цепи. Несимметричный входной сигнал преобразуется в дифференциальный

состоящий из A и A. Каждый из этих компонентов дифференцируется

резистивно-конденсаторной цепочкой – B и B. Далее сигналы преобразуются

компаратором. Неинвертирующий вход компаратора имеет более высокий

потенциал, чем инвертирующий, поэтому на выходе компаратора появляются

сигналы высокого логического уровня, получаемые из узких входных импульсов.

Далее импульсы

поступают на триггер, состоящий из логических элементов «ИЛИ-НЕ». Из

таблицы истинности, показанной на рисунке 2 видно, что схема триггера

инвертирует сигнал: высокий уровень на входе C устанавливает высокий

уровень на выходе D, а высокий уровень на входе C устанавливает высокий

уровень на выходе D.

Длительность

выходных импульсов компаратора невелика, поэтому в течение определенного

времени на выходе компараторов существует низкий логический уровень,

состояние триггера в этом случае не меняется. Выход D подключен к

выходному мультиплексору, т.к. сигнал на нем идентичен входному по форме и

фазе. Если сигнал имеет коэффициент заполнения 0,5 (50:50), импульсы

компаратора симметричны, при коэффициенте заполнения отличном от 0,5,

выходные импульсы компаратора сближаются. |

|

Низкочастотный канал

Как показано на рисунке 3, медленный входной сигнал модулируется

посредством ШИМ высокой несущей частотой. Длительность высокого/низкого

уровня сигнала A находится в отношении 90:10%. В дальнейшем процесс

преобразования асимметричного сигнала идентичен

аналогичному процессу в высокочастотном канале. Для уд аления

высокочастотной составляющей – модулирующей частоты – используется ФНЧ:

R---C-цепочка,устанавливаемая на входе мультиплексора.

Технология

гальванической развязки и основные требования

Успешное

решение проблемы гальванического разделения сигнала для широкой полосы (от

постоянного сигнала до скорости передачи 150 Мбит/с) подвигло TI на выпуск

одно- и двунаправленных модификаций микросхем, содержащих от одного до

четырех каналов (см. рис. 4). Микросхемы могут применяться в

распространенных цифровых интерфейсах в различных промышленных приложениях.

Все микросхемы имеют однополярное питание 3/5 В, логические, КМОП-у ровни

переключения. Номинальное напряжение питания находится в диапазоне 3,3...

5 В и для VCC1, и для VCC2. Возможна различная их комбинация.

Необходимо

помнить, что в силу несимметричной конструкции изоляторы могут применяться

лишь для развязки несимметричного сигнала в 3/5-В цифровых линиях передачи.

На рисунках 5–7 даны примеры использования ЦГР в интерфейсах SPI, RS-2 32

и RS- 485. Обратите внимание, что ЦГР всегда располагаются между

источником данных и приемником или преобразователем независимо от

стандарта интерфейса. На рисунке 5 показан вариант простейшего применения

ЦГР. Входные сигналы — несимметричные, низковольтные. ЦГР используется в

схеме SPI-интерфейса и соединяет контроллер с преобразователем. В

большинстве случаев в SPI-интерфейсах применяются микросхемы ISO72 31 и

ISO72 41, содержащие 3 и 4 канала развязки. На рисунке 6 показана полная

схема интерфейса RS-2 32, в которой используются две четырехканальные

микросхемы: требуется ЦГР для шести служебных сигналов и двух сигналов

передачи данных: TX и RX. Хотя сигналы интерфейса несимметричные, в линии

передачи используется симметричное напряжение ±13 В. Поэтому

между ЦГР и шиной требуется применить специальную микросхему драйвера –

преобразователя сигналов. Также как и в предыду щем примере, ЦГР,

используемая в интерфейсе RS- 485 (см. рис. 7а), включена между

контроллером и шинным преобразователем. Сигналы в интерфейсе низковольтные

и, несмотря на то, что шина дифференциальная, требуется, прежде всего, ЦГР

для несимметричных сигналов. Благодаря простоте интерфейса RS- 485 функции

ЦГР и приемопередатчика можно объединить в одной микросхеме (см. рис. 7б).

Это решение позволяет снизить стоимость системы и уменьшить число

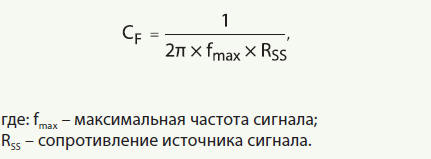

применяемых компонентов. Для упрощения выбора ЦГР в таблице 1 приведены

полные сведения о ЦГР компании TI. Существует пять градаций в зависимости

от скорости передачи: A, B, C, CF, M. Все они, за исключением версии M,

имеют встроенный ФНЧ на входе данных, и поэтому рекомендованы для

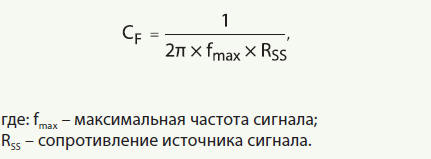

использования в случаях, когда возможны существенные шумы и помехи. В

высокоскоростной версии M для подавления помех может использоваться

внешний ФНЧ. Для этого требуется подключить к входу конденсатор и

соединить его с шиной земли. Величина емкости конденсатора определяется из

выражения:

Рис. 5. Гальваническое разделение интерфейса SPI

Рис. 6. Гальваническое разделение интерфейса RS-232

Рис. 7. Гальваническое разделение интерфейса RS-485

|

| |

|

Поставляемые компоненты

|